學科

乙級學科題庫線上測驗(有未修復的題目錯誤)- 手機 技能檢定題庫 APP

術科

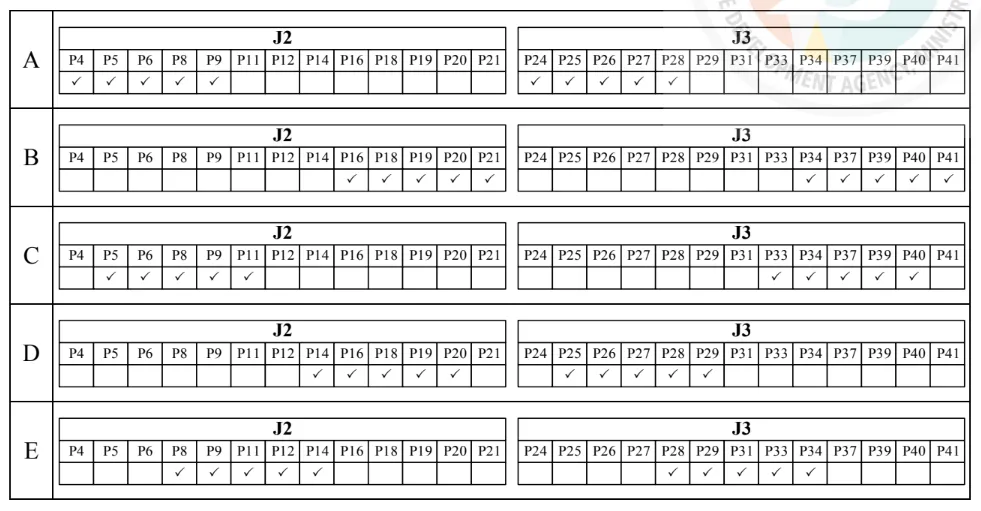

🔹 測試資料

🔹 題目

未使用的規定接角 每隻扣10分

🔹 規範

KiCad 圖框

未完成每項扣10分

Title: [術科測試編號(8碼)]-[崗位編號]

Date: 測試日期

資料夾

未完成每項扣10分

要求在 D:\ 放置兩資料夾

[崗位編號]_CPLD: KiCad 專案[崗位編號]_Layout: Quartus 專案

(建議)

(假設工作崗位為 01)

D:

├── 01_CPLD

│ └── cpld : Quartus 專案

└── 01_Layout

├── layout : KiCad 專案

├── sch_f.pdf : 正面佈線圖

└── sch_b.pdf : 背面佈線圖由於專案名稱不能以 數字 開頭

所以完成後再將整個專案複製進資料夾

🔹 流程

| 內容 | 描述 | 建議花費時間 | |

|---|---|---|---|

| 一 | 檢查材料 | ||

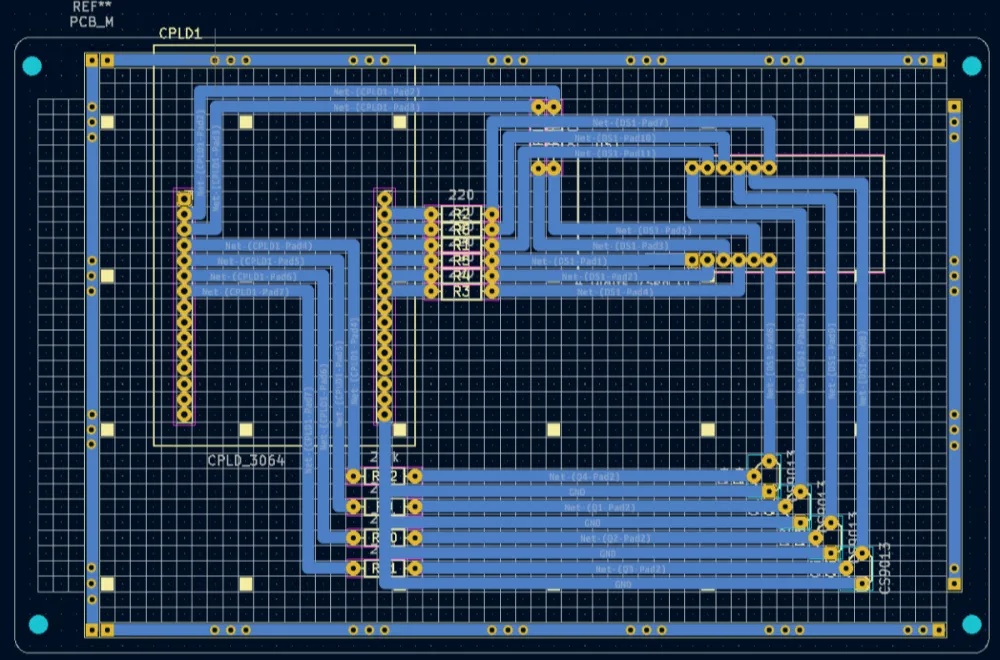

| 二 | KiCad | 1. 原理圖 2. 佈線圖 3. 列印 | < 1 hr |

| 三 | 焊接 | 1. 子板 2. 母板 | < 2.5 hr |

| 四 | Quartus | 1. verilog 2. 腳位配置 3. 燒入 | < 0.5 hr |

| 五 | 評分 |

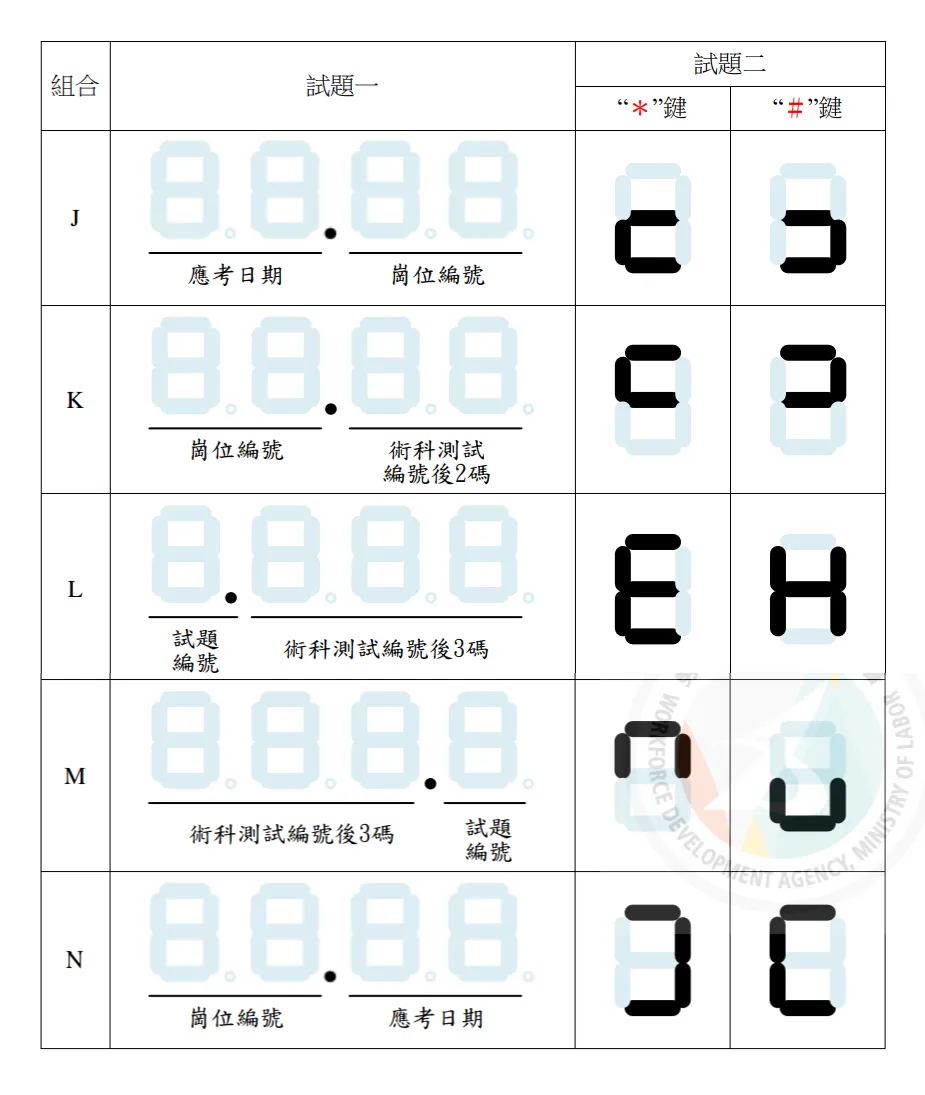

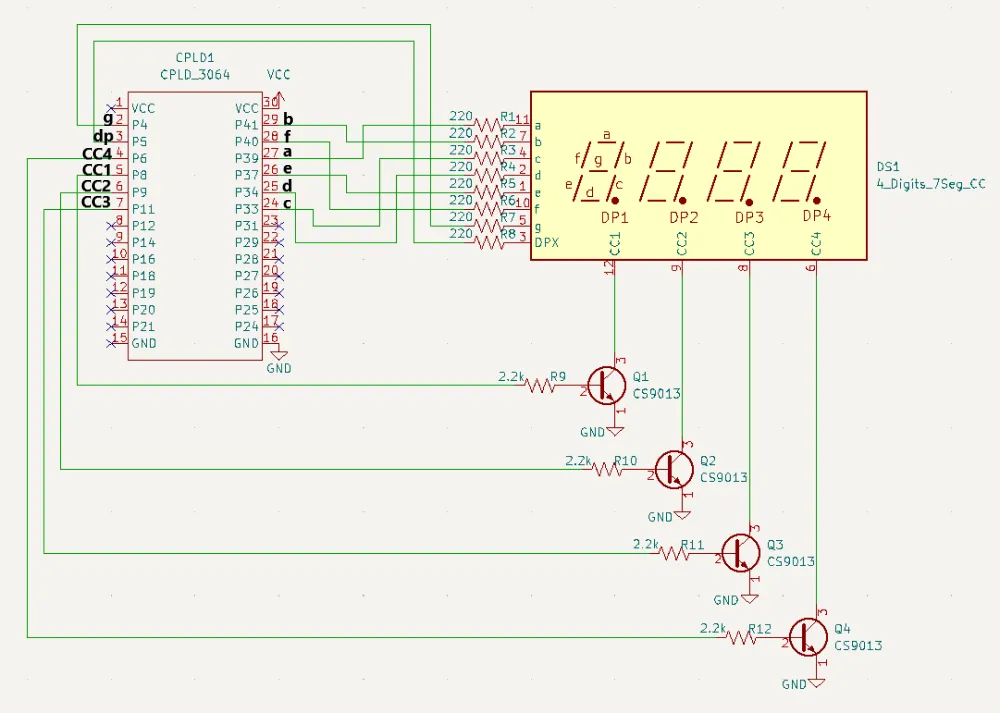

🔸 試題一、四位數顯示

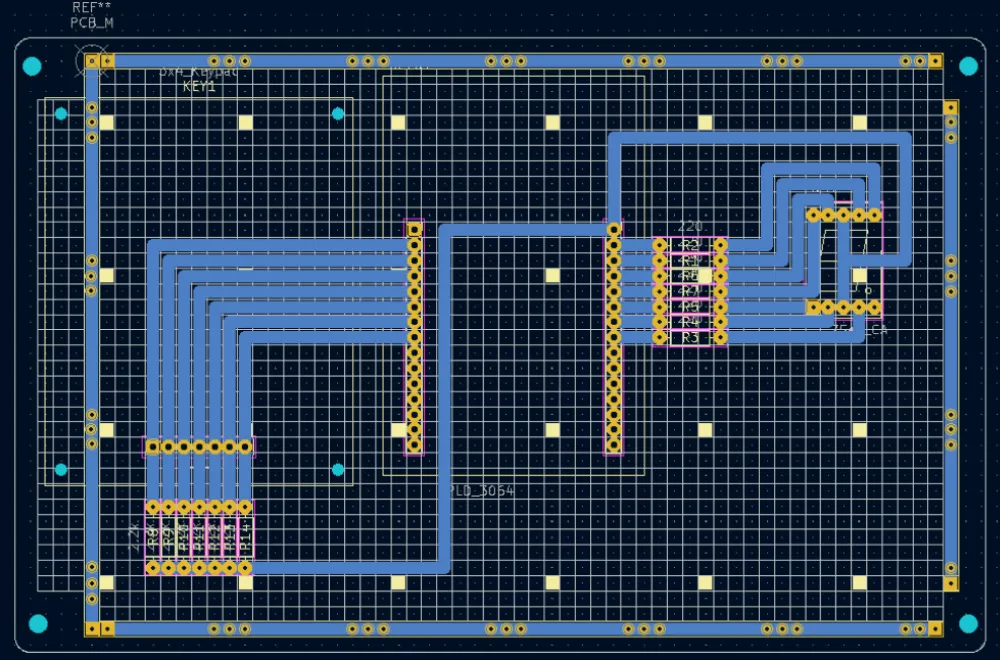

Layout

b f a e d c

g dp

CPLD

共陰極七段顯示:

對於 output reg[6:0] seg

- 1 = ON

- 0 = OFF

module cpld(

input clk,

output reg[3:0] scan

output reg[7:0] seg

);

reg[11:0] div;

always @(posedge clk) begin

div <= div + 1'b1;

end

always @(posedge div[11]) begin

case(scan)

4'b0001: begin scan <= 4'b0010; seg <= 8'b11111111; end // 8

4'b0010: begin scan <= 4'b0100; seg <= 8'b11111111; end // 8

4'b0100: begin scan <= 4'b1000; seg <= 8'b11111111; end // 8

default: begin scan <= 4'b0001; seg <= 8'b11111111; end // 8

endcase

end

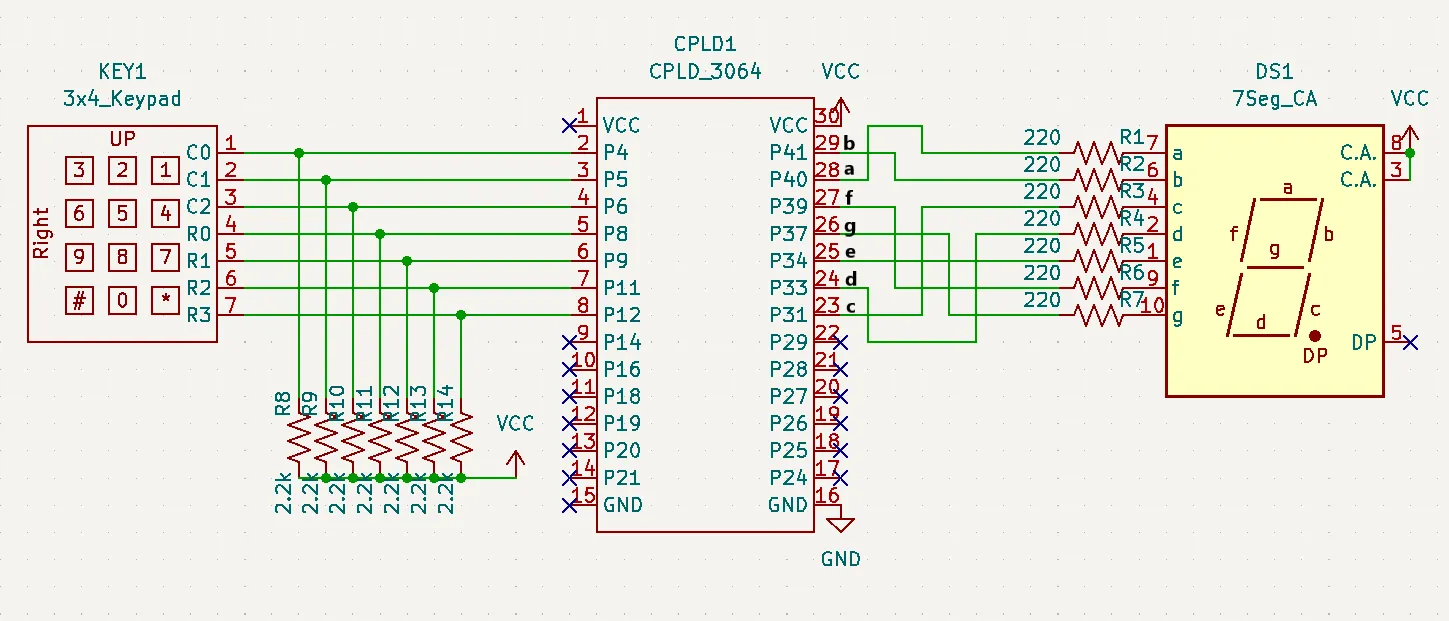

endmodule🔸 試題二、鍵盤輸入顯示

Layout

b a f g e d c

CPLD

共陽極七段顯示:

對於 output reg[6:0] seg

- 0 = ON

- 1 = OFF

module cpld(

input clk,

input [2:0] receive,

output reg[3:0] scan,

output reg[6:0] seg

);

always @(posedge clk) begin

case(scan)

4'b1110: begin

scan <= 4'b1101;

if (receive == 3'b110) seg <= 7'b1001111; // 1

else if(receive == 3'b101) seg <= 7'b0010010; // 2

else if(receive == 3'b011) seg <= 7'b0000110; // 3

end

4'b1101: begin

scan <= 4'b1011;

if (receive == 3'b110) seg <= 7'b1001100; // 4

else if(receive == 3'b101) seg <= 7'b0100100; // 5

else if(receive == 3'b011) seg <= 7'b0100000; // 6

end

4'b1011: begin

scan <= 4'b0111;

if (receive == 3'b110) seg <= 7'b0001101; // 7

else if(receive == 3'b101) seg <= 7'b0000000; // 8

else if(receive == 3'b011) seg <= 7'b0001100; // 9

end

default: begin

scan <= 4'b1110;

if (receive == 3'b110) seg <= 7'b1111110; // -

else if(receive == 3'b101) seg <= 7'b0000001; // 0

else if(receive == 3'b011) seg <= 7'b1111110; // -

end

endcase

end

endmodule